My dream CPU |

|

II. Как работи RCPU.RCPU съдържа целочислен модул – Integer unit, модул за обработка на числа с плаваща запетая Double unit, конвейер за обработка на инструкции – Instruction conveyer, модул за адресни изчисления – Address unit и кеш за инструкции – Instruction cache. Целочислен модул – Integer unit.Модулът за обработка на цели числа има 2 регистъра с общо предназначение rA и rB. В тях може да се пише и чете. Има аритметично – логическо устройство АЛУ, което извършва операции с цели числа. Резултатите от АЛУ постъпват направо в кеш памет от асоциативен тип. На всеки адрес (ред) от тази кеш памет има поле за данни в което се записва резултата от изчислението. Има адресно поле в което се записва изчисленият от адресния модул адрес. Има и флаг който показва валиден ли е адреса в адресното поле. Този флаг е нужен защото в някои операции като например операциите за сравнение между регистрите rA и rB адресът ще е нула. Кеш паметта е организирана и като кръгов буфер. Ако резултата от АЛУ ще се запише в адрес, който вече съществува в кеша се пише върху него. Ако адресът не съществува резултата ще се запише в следващ адрес сочен от брояч. Когато брояча се препълни се нулира сам и сочи началото на кеша. Възможни са и други стратегии за управление на кеш паметта, тази е най-простичката и засега се използва тя. Целочисленият модул е показан на фигура 3. Фиг.3 Блок схема на целочислен модул.

Модул за изчисления с числа с плаваща запетая – Double unitПо-точно това е модул за работа с числа с двойна дължина ( разрядност ). Модулът за работа с числа с плаваща запетая има същата организация и устройство като на целочисления модул. Разликата е, че регистрите са с двойно по-голяма ширина и данновата част на кеша е също с двойна ширина. Освен всичко това той може да извършва и някои целочислени изчисления. Бит в инструкцията посочва как да се интерпретират числата, като цели или с плаваща запетая. Например той може да извърши умножение между младшите половини на регистрите rA и rB. Ако едно двоично число го повдигнем на квадрат, то се побира в регистър с двойна дължина от неговата. Кеш за инструкцииНа адрес в кеша за инструкции има адресна част и част за данни. Също е организиран като кръгов буфер. Първа степен на конвейера за инструкции проверява съществува ли адреса който трябва да прочете в кеша. Ако не, го чете от паметта. Също така всяка прочетена инструкция от първа степен на конвейера се поставя в кеша. Начините за управление на кеш са известни, тук се ползва най-простичката. Модул за адресни изчисления.Модулът за адресни изчисления има 3 базови регистри rBs1, rBs2 I rBs3, 3 индексни регистъра rX1, rX2, rX3 и един регистър за максимална стойност rMaxX. Освен това има и матрица с размер 3 x 3 от 9 регистъра достъпни само за четене. До нея в колона са базовите регистри, а в редица са индексните. Както е показано на фигурата. Така с помощта на 3 суматора в матрицата се съдържат пълна комбинация от суми между индексен и базов регистър. При промяна стойността на един базов регистър например суматорите се превключват и изчиаляват наново цялата редица в матрицата за суми с този базов регистър и съответните индексни регистри. По същия начин ако се промени стойността на индексен регистър суматорите се превключват и се преизчисляват сумите в матрицата в неговата колонка. Това е много удобно при работа с масиви. Например при копиране от масив в масив спестяваме инструкция и време. Тази обвързаност между регистрите може да се включва и изключва. Интересно е да се изнамери и друга реорганизация на тези регистри за други видове удобни изчисления. Регистърът rMaxX се използва от инструкция която прави сравнение с него и посочен индексен регистър. Така се разбира за край на масив и цикъл от тип for се изпълнява много лесно. Друго приложение на този регистър е когато той се зареди с 0. Проверките за нула са много използвани при работа с указатели. В примерите има програма която го демонстрира. Фиг. 4 Модул за адрсни изчисления

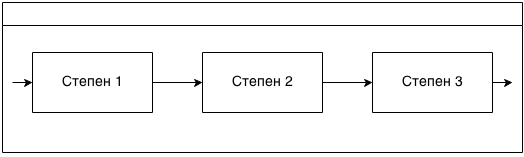

Конвейер за обработка на инструкции.Конвейерът за обработка на инструкции е от три степени. Първа степен прочита цялата инструкция, кода на инструкцията и операнда. Всяка инструкция е разположена на 2 последователни адреса. На първия адрес е кода на инструкцията, на втория е операнда. Изключение е само инструкцията с непосредствено адресиране за конвейера за числа с плаваща запетая. Тя е с дължина 3 адреса, защото числото с плаваща запетая заема 2 последователни адреса. За прочитане на една инструкция са необходими 2 цикъла на системната шина и 3 цикъла за инструкция от 3 последователни адреса. Втора степен на конвейера за обработка на инструкции е най - сложната. Тя получава цялата инструкция от 1-ва степен. Извършва четене от паметта ако е необходимо. Адресът за четене може да е абсолютен, но може да е изчислен и от адресния модул въз основа на указани индексен и базов регистър в инструкцията. Тя може да запише стойност в някой от регистрите на изчислителен или адресния модул. Може да предаде код за изчисление на някой от изчислителните модули. Да предаде адрес и стойност на 3-та степен за запис обратно в паметта. Втора степен извършва и синхронизация между всички модули с които е свързана. Трета степен на конвейера се активира само когато инструкцията е от регистър към паметта, тоест запис на резултат в паметта. Тя е най-простичка. Нейната работа е да извърши запис в паметта. Фиг. 5 Блок схема на конвейера за обработка на инструкциите

Най-голям приоритет за достъп до паметта има 3-та степен, след това е 2-ра и с най-нисък е 1-ва степен. Втора степен на конвейера има и вградена логика за разпознаване на инструкции с преход. Когато разпознае такава инструкция се активира още една паралелна степен на първа. Тя започва четене на данни от адреса за преход който се съдържа в инструкцията. Ако няма преход конвейера си продължава работа със старата 1-ва степен, при преход превключва към алтернативната и прави ресет на ненужната. Това увеличава производителността, защото при преход следващата инструкция е прочетена. Фиг. 6 Блок схема на конвейера за обработка на инструкции с 2 паралелни 1-ви степени

Фиг. 7 Блок схема на целият процесор.

|