My dream CPU |

|

III. Assembler.ADDRESSING METHODSRCPU have only 3 addressing methods: direct, absolute, index addressing.Direct addressing

With this addressing method the number in operand will be assign to any of registers in the CPU. With this addressing kind we can assign direct value in register from integer unit, floating point unit and addressing unit. The instruction length is 2 consecutive addresses in memory, for floating point unit in 3 consecutive addresses. Absolute addressing

In this method the instruction operand is one address, which will be read its value and will be assign to any register in CPU, or back, address in which will be written value from any register. When data flow is from CPU to memory data source could be not a register, could be result from arithmetic or logical calculation. Instruction length is 2 consecutive addresses.

Index addressing

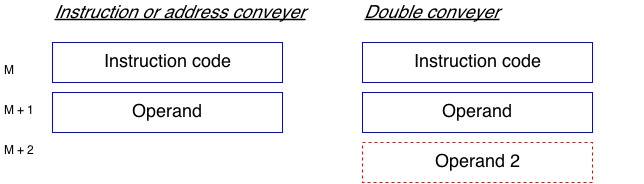

In this kind addressing the address in which will read or write is calculated from sum between base and index register plus instruction operand value. It is possible only index or base value plus instruction operand value. RCPU INSTRUCTIONSThe instruction contain operation code and operand on the next address. Fig. 7 Instruction format.

operation code contain:

1. Instruction Unit ( pipeline ): 2. Direction for data transfer - memory-CPU, CPU-memory, register-register. The arrow shows the direction.

3. Register about the instruction is. In wich will be written or read from it. About I: and D: this are rA and rB. About A: are rBs1, rBs2, rBs3, rX1, rX2, rX3, rMaxX, IP, SP. When data transfer is from CPU to memory are possible the following comands, wich result will be stored in memory:

4. Base and or index register to calc address. This are:

rBs1, rBs2, rBs3, rX1, rX2, rX3

Instruction list for Integer pipelineLoad registers rA и rB.I: rA <-- M[] - load register rA I: rB <-- M[] - load register rB I: rB <-- # - load register rB The arrow is from memory to register. With this instructions is possible direct, index and absolute addressing. Examples: I: rA <-- #5 - load rA with 5. Direct addressing. I: rA <-- M[rBs1, rX1]10 - load rA from memory address calc thru rBs1 + rX1 + 10. Index addressing. I: rB <-- M[]500 - load rB from address 500. Absolute addressing. With sign „ # “ denote direct addressing. With „ M “ memory is used for absolute and index addressing. When between the bracets thera are not registers this is absolute addressing, if there are registers this is index addressing.Store registers in memory:I: rA --> M[, ] - store rA I: rB --> M[, ] - store rB Example:I: rA --> M[, ]500 - store rA in address 500. I: rB --> M[, rX3]0 - store rB in address pointed from rX3 Arithmetic operations:AplsB // rA + rB AmnsB // rA - rB BmnsA // rB- rA AmulB // rA * rB AdivB // rA / rB BdivA // rB / rA Examples: I: AplsB --> M[, rX1]3 The result from calc rA + rB will be stored at address pointed from rX1+3 I: BdivA --> M550 The result from calc rB /rA will be stored at address 550 logical operations:AandB - logical ANDAorB - logical OR AxorB - logical XOR AshlB - SHL, shift left rA thru bits in rB AshrB - SHR, shift right in rA thru bits in rB AshrrB - SHR, shift right in rA with sign thru bits in rB With 32 bit release are used only 5 right bits from rB With 64 bit release are used only 6 right bits from rB Examples: I: AandB --> M[rBs3, rX3] // The calc result from rA and rB will be stored at address pointed from rBs3 +rX3 Branch Instructions:ifAB - Compare registers rA and rB with any condition < , <=, =>, >, == Will be branch if condition is true. Branch could be done on address thru absolute or index addressing. Example: I: if ( A > B ) jump M1000 // If rA > rB branch in address 1000. sortAB - Sort rA and rB. Exchange register values by condition < or >. Branch if: if Exchange – rA and rB war exchanged. if NOT - (if NOT Exchange ) rA and rB war NOT exchanged. Could be used absolute or index addressing. Examples: I: SortAB > ; IfExch M1200 // After instruction execution rA value will be bigger than rB. If there was exchange will be branch on address 1200. I: SortAB > ; IfNoExch M1300 // After instruction execution rA value will be bigger than rB. If there was NOT exchange will be branch on address 1300. Usualy if there is not exchange will be jump over next 2 instructions, wich store rA and rB back in memory. Store back in memory is not needed when they are in natural sort order. This is faster sort. Stack Instructions:Push - store register in stackpop - load register from stack Examples: I: push rA // Store value from rA in stack and decrease SP with 1 I: pop rB // load rB from stack top, inc SP with 1. Floating point unit Instruction listInstructions are the same as for Integer Unit. Logical operations are missing. Stack instructions increase or decrease SP with 2, becouse floating numbers are stored in 2 addresses. The examples are the same, just replace I: with D: Address Unit Instruction listInstructions memory --> register:A: rBs1 <-- M // load register rBs1 A: rBs2 <-- M // load register rBs2 A: rBs3 <-- M // load register rBs3 A: rX1 <-- M // load register rX1 A: rX2 <-- M // load register rX2 A: rX3 <-- M // load register rX3 A: rIP <-- M // load register rIP; Equal to no condition jump A: rSP <-- M // load register rSP; Recommended to use it only in the beginning, CPU establishment. A: rMaxX <-- M //load register rMaxX With all this instructions could be used direct, absolute and index addressing. Instructions register – memory, are the same as memory-register, just the arrow is in back sign. Direct addressing is not possible. Branch Instructions:A: IfMaxX rX1 < rMaxX ; M// If rX1 < rMaxX will be a branch on address. Can be used registers rX1, rX2, rX3. Absolute addressing. Increment:A: IncX rX2 M// Increment register rX2. Possible with registers rX1, rX2, rX3. Direct and absolute addressing. Stack instructions:A: push rX1// Store in stack value from rX1. Could be used all registers from Address Unit without SP. A: pop rX1 // Load from stack rX1. Could be used all registers from Address Unit without SP. A: pushCi // Store Integer constant in stack. A: pushCd // Store Floating number constant in stack. Last 2 Instructions pushCi and pushCd are in group instructions for Address Unit because they change value only in SP and ofcourse stored value in stack. They don't change register in another unit. Instructions register-registerThe Instructions register-register are possible between registers in the same unit and between registers in different units. With Instructions with source Integer unit or Address unit and destination Floating point unit its float part will be 0. With Instructions with source Floating point unit and destination Integer unit or Address unit, fraction part is ignored. Register - register in Integer unit:

In this instruction group are instructions for value transfer between rA and rB and store calc result in register.

Register - register in Floating point unit:The Instructions are the same as in Integer unit, just replace I: with D: Register - register in Address unit:

This Instructions are for sending value in Address unit. Should be carefull when set IP, this is equal to jump instruction. Be carefull set value in SP. Read from IP and SP is not a problem.

Integer unit – Address unit:

Possible between all registers from integer unit and address unit. Address unit - Integer unit:

A: rX1 --> I: rA // rA in Integer unit assept value from rX1 Adress unit. Floating point unit - Address unit:

D: rA --> A: rX1 // Integer part from rA will be assign to rX1 Address unit - Floating point unit:

The value from every register from Address unit ( rBs1, rBs2, rBs3, rX1, rX2, rX3, rMaxX, IP, SP ) can be assign to any of rA or rB, fraction part is ignored. Integer unit – Floating point unit:

Every register ( rA, rB ) or calc result ( AplsB, AmnsB, BmnsA, AmulB, AdivB, BdivA, AandB, AorB, AxorB, AshlB, AshrB, AshrrB ) in Integer unit can be assign to register rA or rB from Floating point unit, fraction part is ignored. Floating point unit - Integer unit:

Value from rA or rB from Floating point unit or its calc result (AplsB, AmnsB, BmnsA, AmulB, AdivB, BdivA,) can be assign to register rA or rB in Integer unit. Integer part only. Some special instructionsInstructions which set value to Instruction pointer IP have some peculiarity. This is equal to jump instruction. When this instruction is in 2 stage on instruction pipeline, after its execution 1-st stage is reset, to avoid instruction execution after it. |